# A ZVS SEPIC WITH MULTI-OUTPUT SOURCES

CHENG-TAO TSAI\*, YING-CHE KUO, YUNG-CHANG LUO AND YING-PIAO KUO

Department of Electrical Engineering National Chin-Yi University of Technology No. 57, Sec. 2, Zhongshan Rd., Taiping Dist., Taichung 41170, Taiwan \*Corresponding author: cttsai@ncut.edu.tw; { kuoyc; luoyc; kuoyp }@ncut.edu.tw

Received October 2016; accepted January 2017

ABSTRACT. In this paper, a zero-voltage-switching (ZVS) single-ended primary inductance converter (SEPIC) with multi-output sources is proposed. The proposed SEPIC has the advantages as follows. 1) The active switches with soft-switching techniques can achieve ZVS under turned-on transitions, resulting in reducing the switching losses and electromagnetic interference (EMI). Therefore, the conversion efficiency of the SEPIC can be increased. 2) To apply the voltage ratio theorem of the transformer, the SEPIC has multi-output sources with step-up and step-down voltage functions. Therefore, the applicability of the proposed SEPIC can be increased. The simulated results have verified that the proposed ZVS SEPIC with multi-output sources has low switching losses and high conversion efficiency.

Keywords: ZVS, SEPIC, EMI

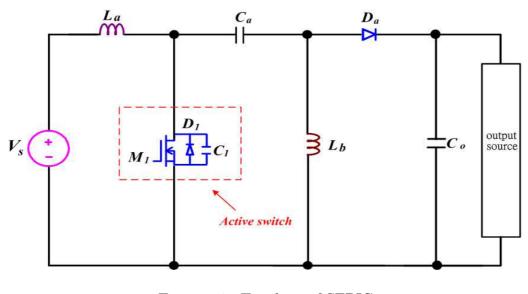

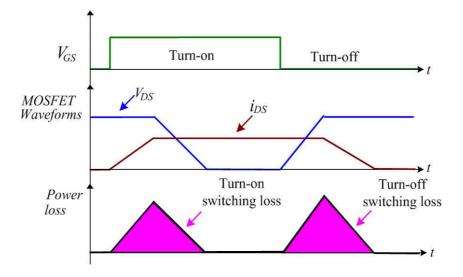

1. Introduction. With the demands for lighter weight, higher efficiency and smaller size, switching power converters have been becoming essential parts of many electronic systems. The voltage and current requirements of these systems often differ radically from the forms, in which the electrical energy is delivered or stored. Switching power converters use power semiconductor devices to control the power flow in an efficient way. A number of non-isolated switching power converters have been developed and proposed. For example, Buck, Boost, 'Cuk, Zeta and SEPIC converters are attracted, which have simple constructions and are widely used in low and medium power. To step-up/down voltage and non-isolated applications, the SEPIC is often adopted, as shown in Figure 1 [1,2]. However, the hard-switching condition of the active switch (MOSFET) is a major contributor to switching losses in the SEPIC, resulting in high power losses, high EMI, and low conversion efficiency [2,3]. The illustration of the hard-switching for the active switch is shown in Figure 2. To overcome these disadvantages, the SEPIC with soft-switching techniques is usually the first choice [3,4].

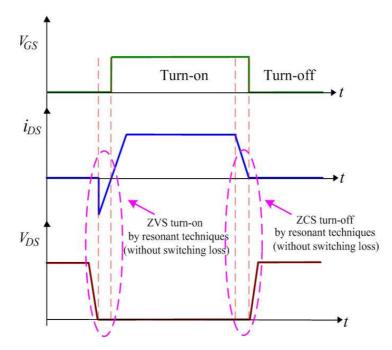

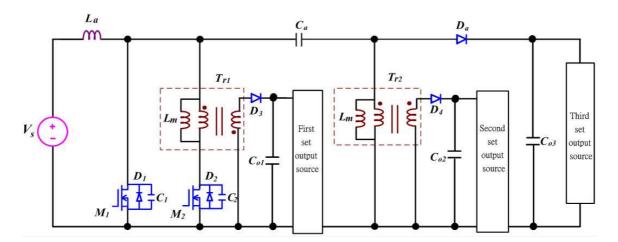

In general, the soft-switching techniques can be classified into ZVS and zero-currentswitching (ZCS) techniques [5-7]. The ZVS or ZCS technique drives the voltage or current of the active switch to zero before any switching action, and avoids the concurrent high voltage and high current in the switching transition, as shown in Figure 3. Therefore, soft-switching techniques are effective means to solve or alleviate switching losses, stresses and EMI problems. In comparison of ZVS and ZCS techniques, the ZVS techniques have simpler structures and easier designs [6-8]. In this paper, a ZVS SEPIC with multi-output sources is proposed, as shown in Figure 4. The proposed SEPIC has the advantages as follows: 1) high conversion efficiency, 2) low EMI emissions, and 3) multi-output sources. The operational principles of the proposed ZVS SEPIC are decribed in Section 2. Simulated and experimental results obtained from the proposed ZVS SEPIC with multi-output sources are presented in Section 3. Finally, a conclusion is given in Section 4.

FIGURE 1. Topology of SEPIC

FIGURE 2. Turn-on and turn-off transition waveforms of a MOSFET

2. **Operational Principles.** As shown in Figure 4, the proposed ZVS SEPIC consists of main switch  $(M_1)$ , auxiliary switch  $(M_2)$ , transformers  $(T_{r1} \text{ and } T_{r2})$ , free-wheeling diodes  $(D_a, D_3 \text{ and } D_4)$  and filter capacitors  $(C_a, C_{o1}, C_{o2} \text{ and } C_{o3})$ . The ZVS cell is composed of auxiliary switch  $(M_2)$  and transformer  $T_{r1}$  to achieve the ZVS features of the main and auxiliary switches  $(M_1 \text{ and } M_2)$ . To apply the voltage ratio theorem of the transformers  $(T_{r1} \text{ and } T_{r2})$ , the proposed SEPIC has multi-output sources with step-up and step-down voltage functions. Therefore, the utility of the proposed ZVS SEPIC can be increased.

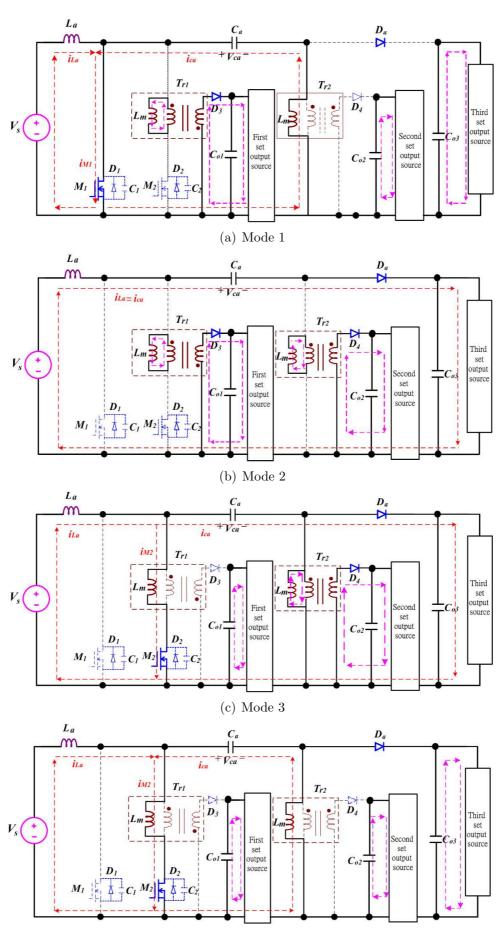

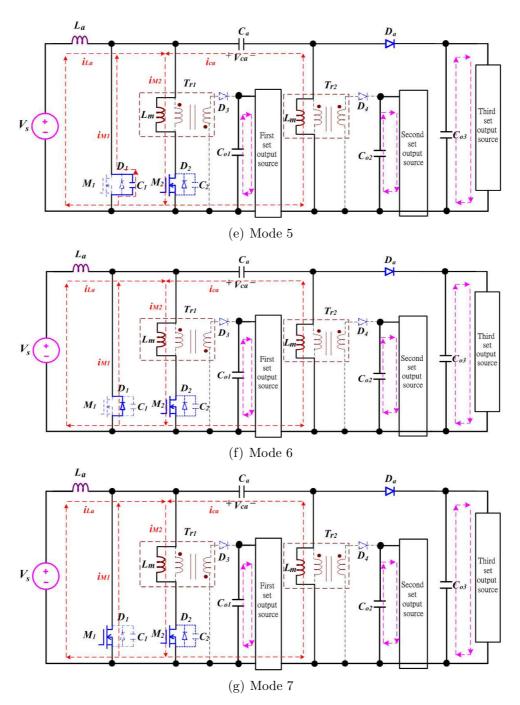

In Figure 4, the operational principles of the ZVS SEPIC with multi-output sources over one switching cycle can be divided into seven major operating modes. Figure 5 shows the equivalent circuit modes of the ZVS SEPIC with multi-output sources over a switching cycle. To simplify description of the operational modes, the following assumptions are made.

- 1) Capacitance of  $C_a$ ,  $C_{o1}$ ,  $C_{o2}$  and  $C_{o3}$  is large enough so that the voltages across them are constant over a switching cycle.

- 2) All of the switching devices, MOSFETs and diode are ideal.

### Mode 1, Figure 5(a):

At mode 1, main switch  $(M_1)$  is turned on and auxiliary switch  $(M_2)$  is turned off. Inductor current  $i_{La}$  flowing through the path of  $V_s$ - $L_a$ - $M_1$  is linearly increased. While

FIGURE 3. Illustration of ZVS and ZCS techniques for a MOSFET

FIGURE 4. Topology of ZVS SEPIC with multi-output sources

capacitor  $(C_a)$  is discharged, discharging current  $i_{ca}$  is flowing through the path of  $C_a$ - $M_1$ - $T_{r2}$ . At this time, the current  $i_{M1} = i_{La} + i_{ca}$ . During this mode, magnetic inductance  $(L_m)$  of transformer  $(T_{r1})$  delivers power to first-set source, and capacitors  $(C_{o2} \text{ and } C_{o3})$  individually deliver power to secondary-set and third-set output sources. The equivalent circuit is shown in Figure 5(a).

### Mode 2, Figure 5(b):

At mode 2, main switch  $(M_1)$  is turned off, and auxiliary switch  $(M_2)$  is maintained off. While diode  $(D_a)$  is turned on, inductor current  $i_{La}$  begins discharging and flowing through the path of  $L_a$ - $C_a$ - $D_a$ - $V_{o3}$ - $V_s$ . During this interval, magnetic inductance  $(L_m)$  of transformers  $(T_{r1} \text{ and } T_{r2})$  individually deliver power to first-set and secondary-set sources and capacitor  $(C_{o3})$  continuously deliver power to third-set output source. The equivalent circuit is shown in Figure 5(b).

### Mode 3, Figure 5(c):

At mode 3, auxiliary switch  $(M_2)$  is turned on under ZVS condition and main switch  $(M_1)$  is maintained off. Inductor current  $i_{La}$  is divided into two-branch currents  $i_{M2}$  and

FIGURE 5. Equivalent circuits of ZVS SEPIC with multi-output sources

$i_{ca}$ , one is flowing through the path of  $L_a$ - $C_a$ - $D_a$ - $V_{o3}$ - $V_s$ , and the other is flowing through the path of  $L_a$ - $T_{r1}$ - $M_2$ - $V_s$ . During this interval, capacitor ( $C_{o1}$ ) delivers power to first-set source. Magnetic inductance ( $L_m$ ) of transformer ( $T_{r2}$ ) delivers power to secondary-set source. The equivalent circuit is shown in Figure 5(c).

## Mode 4, Figure 5(d):

At mode 4, when current  $i_{La} = i_{M2}$ , diode  $(D_a)$  is turned off. Then, capacitor  $(C_a)$  begins discharging through the path of  $C_a$ - $T_{r1}$ - $M_2$ - $T_{r2}$ . At this time, the current  $i_{M2} = i_{La} + i_{ca}$ . During this interval, capacitors  $(C_{o1}, C_{o2} \text{ and } C_{o3})$  individually deliver power to first-set, secondary-set and third-set sources. The equivalent circuit is shown in Figure 5(d).

### Mode 5, Figure 5(e):

At mode 5, when current  $i_{La}$  is less than  $i_{M2}$ , parasitic capacitance  $(C_1)$  of main switch  $(M_1)$  is discharged. At this time, the current  $i_{M2} = i_{La} + i_{M1} + i_{ca}$ . During this interval, capacitors  $(C_{o1}, C_{o2} \text{ and } C_{o3})$  individually deliver power to first-set, secondary-set and third-set sources. The equivalent circuit is shown in Figure 5(e).

### Mode 6, Figure 5(f):

At mode 6, voltage of parasitic capacitor  $(C_1)$  is dropped to zero, and body diode of main switch  $(M_1)$  is conducting and creating a ZVS condition for main switch  $(M_1)$ . At this time, the current  $i_{M2} = i_{La} + i_{M1} + i_{ca}$ . During this interval, capacitors  $(C_{o1}, C_{o2}$ and  $C_{o3}$ ) individually deliver power to first-set, secondary-set and third-set sources. The equivalent circuit is shown in Figure 5(f).

### Mode 7, Figure 5(g):

At mode 7, main switch  $(M_1)$  is turned on under ZVS conduction. At this time, the current  $i_{M2} = i_{La} + i_{M1} + i_{ca}$ . During this interval, capacitors  $(C_{o1}, C_{o2} \text{ and } C_{o3})$  individually deliver power to first-set, secondary-set and third-set sources. The operational mode of the converter over one switching cycle is completed. The equivalent circuit is shown in Figure 5(g).

3. Simulated and Experimental Results. To verify the feasibility, the simulated circuit of the proposed ZVS SEPIC with multi-output sources is built. Its specifications are listed as follows:

- input voltage: 100  $V_{dc}$ ,

- first-set output voltage: 5  $V_{dc}$ ,

- second-set output voltage:  $24 V_{dc}$ ,

- third-set output voltage: 400 V<sub>dc</sub>,

- total output power: 150 W, and

- switching frequency: 50 kHz.

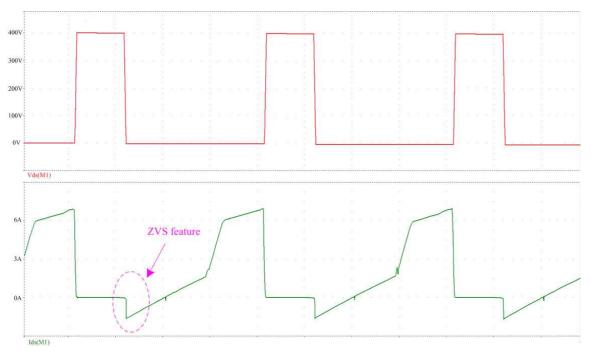

Figure 6 shows simulated voltage and current waveforms of the main switch  $M_1$  at turnon transition for ZVS SEPIC. From Figure 6, it can be seen that the main switch  $M_1$

$(V_{ds}: 100 \text{ V/div}; i_{ds}: 3 \text{ A/div}; \text{Time: } 5 \mu \text{s/div})$

FIGURE 6. Simulated voltage and current waveforms of the main switch  $M_1$

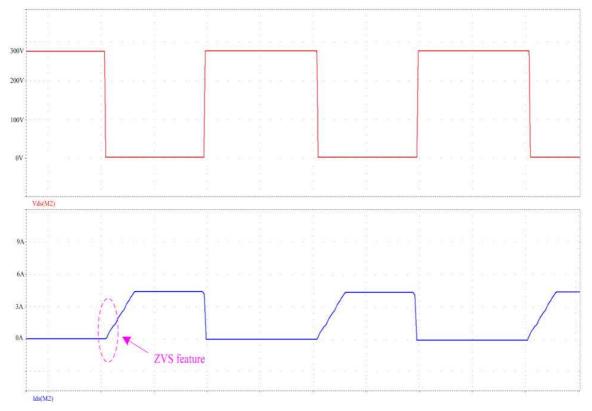

$(V_{ds}: 100 \text{ V/div}; i_{ds}: 3 \text{ A/div}; \text{Time: } 5 \mu \text{s/div})$

FIGURE 7. Simulated voltage and current waveforms of the auxiliary switch  $M_2$

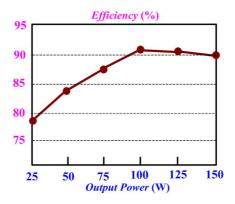

FIGURE 8. Efficiency of the proposed ZVS SEPIC under full-load condition

has a ZVS feature. Figure 7 shows simulated voltage and current waveforms of auxiliary switch  $M_2$  at turn-on transition for ZVS SEPIC. From Figure 7, it can be seen that the auxiliary switch  $M_2$  has also a ZVS feature. The efficiency values of the ZVS SEPIC by formulas are obtained in Figure 8, in which it can be seen that the maximum efficiency can be reached as high as 90% under full-load condition. Therefore, the proposed ZVS SEPIC with multi-output sources has high conversion efficiency.

4. Conclusions. In this paper, a ZVS SEPIC with multi-output sources is proposed. The proposed ZVS SEPIC uses transformers  $(T_{r1} \text{ and } T_{r2})$  and auxiliary switch  $(M_2)$  to implement the features of ZVS and multi-output sources. Therefore, the switching losses of main and auxiliary switches can be reduced, and the efficiency of the proposed ZVS SEPIC can be increased. In addition, to apply the voltage ratio theorem of the transformers  $(T_{r1} \text{ and } T_{r2})$ , the proposed SEPIC has multi-output sources with step-up and step-down voltage functions. Therefore, the utility of the proposed ZVS SEPIC can be increased. Simulated results have verified that the proposed ZVS SEPIC with multioutput sources is relatively suitable for the applications of step-up/down output voltages and high conversion efficiency.

#### REFERENCES

- D. S. L. Simonetti, J. Sebastian and J. Uceda, A small-signal model for SEPIC, Cuk and flyback converters as power factor preregulators in discontinuous conduction mode, *The 24th Annual IEEE Power Electronics Specialists Conference*, pp.735-741, 1993.

- [2] P. J. S. Costa, C. H. I. Font and T. B. Lazzarin, Improvement of stability in current-programmed SEPIC DC/DC converters, *IEEE the 13th Brazilian Power Electronics Conference and the 1st South*ern Power Electronics Conference (COBEP/SPEC), pp.1-6, 2015.

- [3] B. Axelrod and Y. Berkovich, New coupled-inductor SEPIC converter with very high conversion ratio and reduced voltage stress on the switches, *IEEE the 33rd International Telecommunications Energy Conference (INTELEC)*, pp.1-7, 2011.

- [4] X. Wu, J. Zhang, X. Ye and Z. Qian, Analysis and derivations for a family ZVS converter based on a new active clamp ZVS cell, *IEEE Trans. Ind. Electron.*, vol.55, pp.773-781, 2008.

- [5] C. K. Unnikrishnan and C. R. Raj, High frequency Quasi resonant SEPIC converter for wide range of operation, *International Conference on Circuit, Power and Computing Technologies*, pp.984-989, 2014.

- [6] F. Ongaro and S. Saggini, ZVS isolated active clamp Sepic converter for high power LED applications, The 27th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp.957-962, 2012.

- [7] B.-R. Lin, K.-L. Shih, J.-J. Chen and H.-K. Chiang, Implementation of a zero voltage switching Sepic-Cuk converter, *The 3rd IEEE Conference on Industrial Electronics and Applications*, pp.394-399, 2008.

- [8] H.-L. Do, Soft-switching SEPIC converter with ripple-free input current, IEEE Trans. Power Electronics, pp.2879-2887, 2012.